어제 Paging과 관련하여 해결되었다고 생각했었는데,

한가지 문제가 해결이 안되네요.

주석 넣는 건 완료했고요,

file을 하나씩 올렸더니, Rev 21까지 올려놨네요.-_-;

참석자 이름을 다 넣으려고 하다가 Paging 정리하고 도저히 못하겠어서, 다음으로 넘겼습니다.

PAE paging Intel manual을 보면 Logical Address Translation이

PDPTE -> PDE -> PTE 이런 순서로 되어있는데요.

PDPTE 1 page : 8byte

PDE 1 page : 32byte

PTE 4 page : 2MB Page

이렇게 된다고 보았고요.

0x1007이 PDPTE, 0x1007이 PDE, 0x183 + 0x200000이 PTE와 같이 초기화 된다고 생각했습니다.

그래서 관련된 내용을 적으려고 했더니,

PDPTE entry가 좀 문제가 생기네요.

PDE는 우리가 생각한 대로 그대로 인데요.

PDPTE는 0 bit는 맞는데 2-3 bit가 reserved로 반드시 0으로 초기화 되어야 하여

0x1007이라는 값이 맞질 않습니다. (만약, 억지라도 넣는다면 Page Fault가 발생하게 되더라고요..)

관련된 내용을 좀 더 보완해야할 것 같네요.

혹시 주석이나 관련 내용을 찾아보시고 제가 잘못 이해한 것이거나,

문제를 해결한 분이 있다면 알려주시길 부탁드릴께요.

댓글 6

-

도영주

2013.10.07 00:23

추천:2 댓글

-

홍석85

2013.10.07 20:13

두분 자세한 설명 감사 드립니다 :)

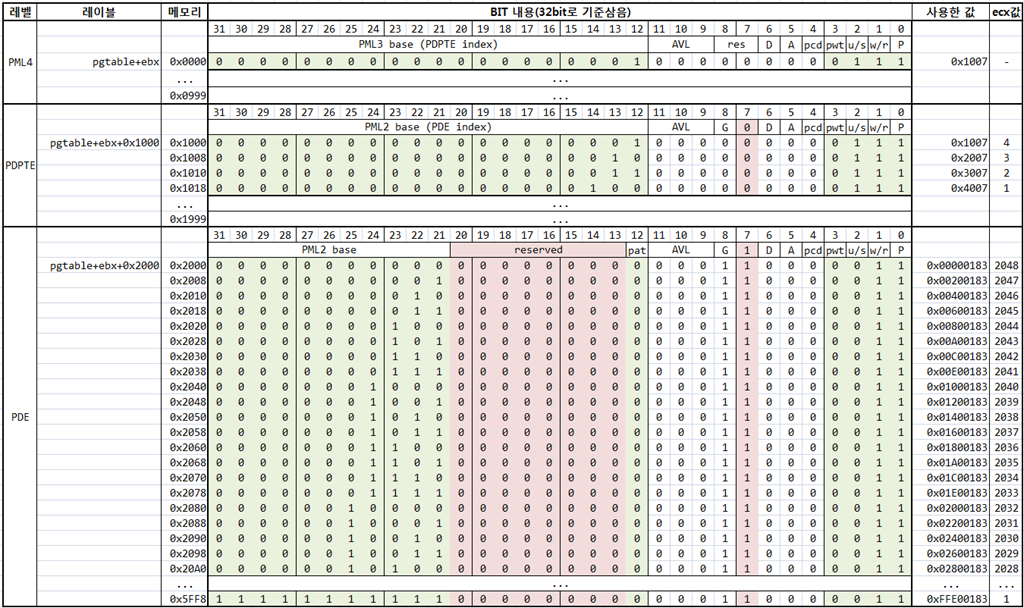

표로 한번 그려봤는데 윗 두분께서 말씀해주신 내용이 잘 맞아떨어지고 메뉴얼과도 잘 맞네요.

indexing이 0부터 시작하지 않는다는 것에 좀 눈이 팔려 있었는데...

IA-32e paging중 2MB페이지에 대한 제약사항들과(레퍼런스가 있네요.)

메모리가 4KiB로 정렬되어있다는 점, PML4, PDPTE, PDE각 각각 1,1,4개의 page(각 4KiB)로 되어있는

전제조건으로 인해 1부터 indexing이 가능하다는 점을 이제야(ㅋㅋ) 이해하게 되었네요.ㅠ

아, 정말 공부해야 할 것이 많음을 느낍니다.

공부하면서 작성한 표를 첨부합니다.

의미가 있는셀은 초록색, 해당 단계에 반드시 있어야하는 규칙은 붉은색으로 표현했습니다.

저처럼(또 있을까..) 헤맨 분들에게 도움이 되면 좋겠네요 :)

그럼 토요일에 뵐께요!

-

조동현

2013.10.07 17:09

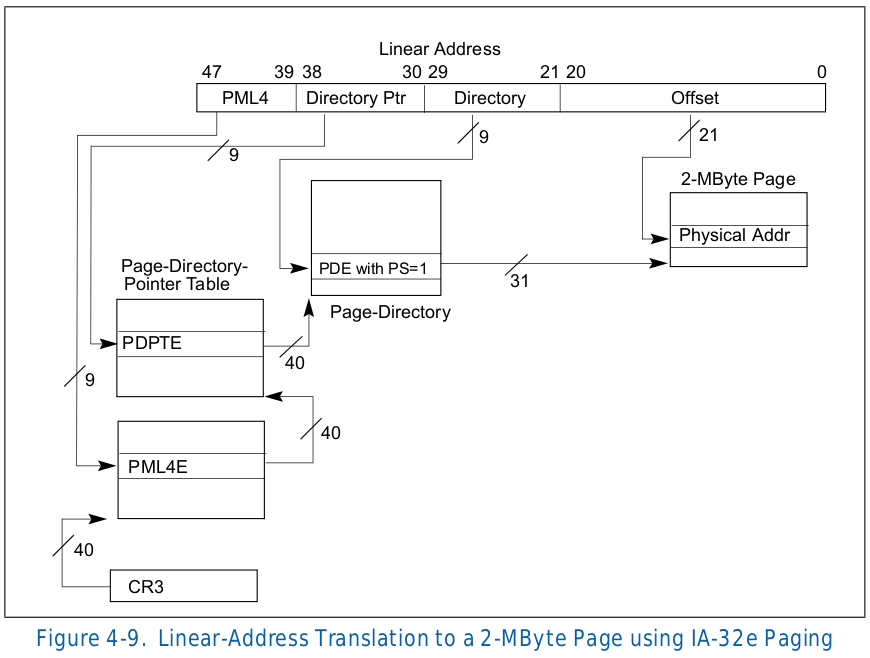

인텔 메뉴얼을 찾아보니, 저희는 Intel에서 지원하고 있는 세가지 모드 중 IA-32e 를 사용하고 있더라구요.

2MB 페이징을 하게되면 위 그림과 같이 9bit + 9bit + 9bit + 21bit(2MB) 로 나뉘어서 페이징을 하게 됩니다.

소스코드에 주석으로 있던 Level 4/3/2가 각각 9bit씩 맡고 페이징을 하게 되는 것이죠.

말씀하신 0x1007은 현재 PDPTE의 시작 주소를 나타내고 있는 것은 맞습니다. 여기서부터 2^9(512)개의 페이지 엔트리(8byte) 가 모여서 하나의 페이지를 이루게 됩니다.

Linear-Address 를 Translation하는 과정에서 CPU는 현재 offset (인덱싱할 9bit)을 가지고 0x1007 에 위치하고 있는 페이지에서 인덱싱을 하게 됩니다.

예를 들면 Linear-Address의 38...30 bit가 0x02라고 하면, 다음 bit(29...21)들의 인덱싱을 담당하고 있는 PDE는 0x1007+0x02*8byte에 위치하고 있게 되는 페이지 엔트리에서 설명하고 있는 주소로 가봐라.. 라는 것이죠..

일단 소스코드랑은 다 맞아 떨어지는 것 같은데.. 여전히 다시 보면 헷갈리는군요 ㅎㅎ

즐거운 한 주 보내시고 토요일에 뵈요!

-

홍석85

2013.10.07 13:07

그렇지 않아도 토요일날 마지막시간에 페이징관련된 부분이 정리가 안되서ㅎㅎ

어제 쭉 그려봤는데요,

저희가 공부한 OS 커널의 구조와 원리에 나온 페이징기법 구현부분에 따라 맞춰봤었습니다.

아직 잘 이해가 안가서 달아주신 링크를 보고 있는데요,

디렉토리엔트리(1Kib, 1entry) -> 디렉토리엔트리(1Kib, 4entry) -> 페이지엔트리(4Kib, 4096entry)로 구성되는 것까지는

이해가 되는데,, 0x1007일때 앞의 1이 entry index로 여겨지는데

이게 왜 0부터 시작되지 않고 1부터 index가 시작되는지 명확하게 이해가 안가네요.

나중에 정리하시면 꼭 올려주세요. :)

-

이경욱

2013.10.07 18:18

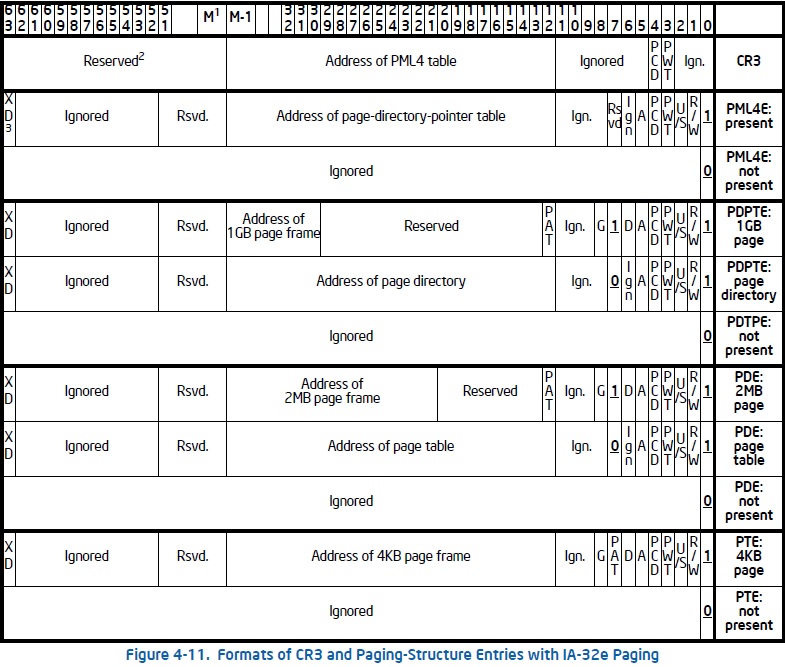

현재 소스에서 사용하는 페이징은 4단계 페이징입니다

4단계 페이징은 다음과 같은 총 3개의 엔트리를 가집니다

PML4E (Page Map Level4 Table Entry)

PDPTE (Page Directory Pointer Table Entry)

PDE (Page Directory Entry)

(5단계 페이징엔 Page Table Entry가 추가됩니다)

Build Level 4 라고 적힌 곳에서 PML4E를 세팅해주고

Build Level 3 에서는 PDPTE를

Build Level 2 에서는 PDE를 세팅해줍니다

Level 4 와 3의 0x1007에서 1은 위의 그림에 나와있는 Address of page-directory-pointer table과

Address of page directory의 값을 세팅하기 위해 더해주는 것이고

Level 2의 0x00200000씩 더해주는 코드는 Address of 2MB page frame의 값을 세팅하기 위함입니다

홍석님의 댓글에서

0x1007을 더해줄때 1의 의미는 현재 엔트리는 다음 엔트리의 주소를 가지고 있어야 하는데

0x0007만 더해주면 현재 엔트리를 가리켜 버리게 되므로 4k만큼의 주소를 더해주는 것입니다

여기까지가 제가 이해한 부분입니다!

추천:1 댓글

-

도영주

2013.10.07 19:39

와 이사람들 공부 많이 했네 ㅋㅋ

우선 이경욱님 정답!!!!

이걸 주석으로 달려다가 포기했는데 ㅋㅋ

휴일에 주석달아서 up할께요.

한가지 더 해서 저번에 말씀드린것 처럼

이메일 주소 밴드로 좀 보내주세요!!

이름 좀 남겨보자구요ㅋ

처음에 PAE mode만 활성화해서

PAE 3-level에서 헤맸던게 실수더군요.

PAE 4-level은 lme를 설정해줘야하고요.

이건 정리해 드릴께요.

IA-32e paging안에 있고,

이경욱 님이 남기신 댓글에 답이 나와있어요.

코드 주석 남긴 스타일도 한번 봐주세요.

댓글이 많이 달리니 기분이 매우 좋군요!!

.

해결 했네요. ㅋㅋㅋㅋ

http://www.sandpile.org/x86/paging.htm

PAE paging 이 아니라,

IA-32e Paging system 이었군요.

다시 정리해야할 것 같은데, 시간이 엄청 오래 걸릴 것 같아서,

휴가일에 적어보도록 하겠습니다.

해결하고 났더니 개운하네요 ㅋㅋㅋㅋ