8.4 MULTIPLE-PROCESSOR (MP) INITIALIZATION

IA-32 아키텍처는 ( P6 패밀리 프로세서부터 시작된 ) 다중프로세서(MP) 초기화 프로토콜을 정의하고 Multiprocessor Specification Version이라고 부른다. 이 명세서는 IA-32 다중프로세서 시스템에서 boot 프로토콜을 정의한다. MP 초기화 프로토콜 다음과 같은 중요한 특징이 있다 :

• 시스템 하드웨어에 전용 요청이 없이 다중프로세서의 부팅 제어를 지원한다.

• 시스템이 부팅되면서 하드웨어를 초기화 하는 것이 signal 에 의존 혹은 부트 프로세서에 미리 정의됨 없이 가능케 한다.

• IA-32 프로세들은 같은 방법으로 부트되고 이는 Intel Hyper-Threading 기술을 포함한다.

• MP 초기화 프로토콜은 또한 Intel 64프로세서의 사용에도 적용된다.

MP 초기화 프로토콜의 IA-32 프로세서 패밀리별 차이점은 다음과 같습니다 :

• For P6 family processors — BSP와 APs 의 selection 은 (see Section

8.4.1, “BSP and AP Processors”) APIC 버스에서 BIPI 와 FIPI 메시지를 사용한 중재로 제어된다.

See Appendix C, “MP Initialization For P6 Family Processors,”

for a complete discussion of MP initialization for P6 family

processors.

• Intel Xeon processors with family, model, and stepping IDs up to F09H —

위와 동문. The selection of the BSP and APs (see Section 8.4.1, “BSP and AP Processors”) is

handled through arbitration on the system bus, using BIPI and FIPI messages

(see Section 8.4.3, “MP Initialization Protocol Algorithm for

Intel Xeon Processors”).

• Intel Xeon processors with family, model, and stepping IDs of F0AH and

beyond, 6E0H and beyond, 6F0H and beyond — BSP와 APs 의 selection 은 (see Section

8.4.1, “BSP and AP Processors”) BIPI 와 FIPI의 중재에 의함이 아닌 특별한 시스템 버스 사이클에 의해 제어된다.

(see Section 8.4.3, “MP Initialization Protocol Algorithm for Intel Xeon Processors”).

패밀리, 모델, 스테핑 ID는 CPUID 명령을 EAX 레지스터 값 1 과 함께 실행시켰을 때 EAX레지스터로 받을 수 있다.

8.4.1 BSP and AP Processors

MP 초기화 프로토콜은 두 프로세서의 두 클래스를 정의했다 : the bootstrap processor (BSP) 와 the application processor (APs). 전원인가나 Reset에 따라 MP system은 동적으로 시스템 버스상의 하나의 프로세서를 BSP로 삼는다. 남은 프로세서들은 APs로 지정된다.

BSP 선택 메카니즘의 부분으로, BSP flag 가 IA32_APIC_BASE_MSR( see Figure 10-5 ) 가 세팅되고, 이것이 BSP를 나타낸다. 이 flag는 다른 프로세서들에서는 clear된다. BSP 는 BIOS의 boot-strap 코드를 수행해 APIC 환경을 설정하고, 시스템-wide 데이터 구조체들을 설정하고, APs 들의 초기화를 시작한다. BSP와 APs 가 초기화 됐을때, BSP는 운영체제-시스템 초기화 코드를 실행한다.

전원인가나 reset에 따라, APs는 최소한의 자가-설정을 완료하고, startup signal ( a SIPI 메시지 ) 가 BSP 프로세서로부터 오기를 기다린다. SIPI 메시지를 전달받은 후에, AP는 BIOS AP 설정 코드를 실행하고, which ends with the AP being placed in halt state.

Intel 64 와 IA-32 프로세서들을 위해 Intel Hyper-Threading 기술( 이하 HT ) 이 지원되고, MP 초기화 프로토콜은 시스템 버스 상의 논리적 프로세서들이나 논리적연결영역으로(coherent link domain) 구분되는 프로세서( 유일 APIC ID와 함께 ) 들 각각 대우한다. Bootup 되는 동안 하나의 논리적 프로세서가 BSP로 선택되고 남은 논리 프로세서가 Aps로 지정되게 된다.

8.4.2 MP Initialization Protocol Requirements and Restrictions

MP 초기화 프로토콜은 다음의 시스템 요구조건과 제약사항들을 강요한다.

• MP 프로토콜은 전원인가나 RESET 이 된 후에만 실행되야 한다. 만약 MP 프로토콜이 완료되고 BSP가 선택되어 있다면, 다음 INITs( 특정 프로세서나 시스템광범위하게 ) 에서 MP 프로토콜이 반복되면 안된다. 대신 각 논리적 프로세서는 자신의 BSP flag(in the IA32_APIC_BASE MSR )를 검사하고 자신이 BIOS boot-strap code를 실행하던가 ( 만약 자신이 BSP라면 ) wait-for-SIPI 상태( 만약 자신이 AP라면 ) 가 될 것인지를 결정한다.

• 시스템의 모든 인터럽트를 전달시킬 능력이 있는 디바이스들은 MP 초기화 프로토콜의 진행 동안에는 억제된다. BSP가 INIT-SIPI-SIPI 를 AP에게 순서대로 발생시키고 마지막 SIPI 흐름에 대한 응답이 있을 때까지의 시간이 흐르는 동안 인터럽트들은 억제된다.

8.4.3 MP Initialization Protocol Algorithm for Intel Xeon Processors

전원인가나 RESET이 MP 시스템에서 발생함에 따라, 시스템의 프로세서들은 MP 초기화 프로토콜 알고리즘을 실행해 각 시스템 버스 상의 논리적 프로세서와 논리적연결영역의 프로세서들을 초기화한다. 이 알고리즘을 수행하는 과정에서 다음에 오는 boot-up 과 초기화 동작들이 수행된다 :

1. 각 논리적 프로세서는 시스템 topology에 기반한 유일한 APIC ID를 배정받는다. 이 유일ID는 프로세서가 CPUID의 0BH 구문을 지원한다면 32-bit 값을 갖고 아닌 경우에는 8-bit 값을 갖는다.

(see Section 8.4.5, “Identifying Logical Processors in an MP System”).

이 ID는 각 프로세서의 local APIC ID 레지스터에 기록된다.

2. 각 논리적 프로세서는 자신의 APIC ID에 기준해 유일한 중재 우선순위 값을 갖는다.

3. 각 논리적 프로세서는 그들의 내부 BIST 를 시스템 버스 상의 다른 프로세서들과 동시에 실행한다.

4. BIST 가 완료된 후에, 논리적 프로세서들은 하드웨어-정의에 따른 선택 메커니즘으로 BSP와 Aps를 사용 가능한 시스템 버스 상의 논리 프로세서에서 선택한다. BSP 선택 메커니즘은 family, model, F0AH의 stepping ID 에 따라 다르다. 계속해서 보면 :

— Family, model, and stepping IDs of F0AH and onwards:

• 논리적 프로세서들은 BNR# signal을 모니터링 하기 시작하는데 이는 toggling이다. BNR# pin이 toggling을 멈췄을 때, 각 프로세서는 NOP 이라는 특별한 사이클을 시스템 버스에 발생시킨다.

• 최고의 중재 권한을 가진 논리적 프로세서가 특별한 NOP 사이클을 발생시키고 BSP로 임명된다. 이 프로세서는 BSP flag( IA32_APIC_BASE MSR ) 을 세팅하고, 그 뒤에 BIOS boot-strap code의 fetch와 실행이 이뤄지고, 시작지점은 reset vector이다 ( 물리 주소 FFFF FFF0H )

• 남은 논리 프로세서들은 ( NOP발생에 실패한 ) Aps로 설정된다. 그들은 자신들의 BSP flag 를 clear 상태로 만들고 “wait-for-SIPI 상태” 로 돌입한다.

— Family, model, and stepping IDs up to F09H:

• 각 프로세서는 “자신의 모든 것을 포함한” BIPI를 방송한다. 가장 먼저 BIPI를 방송한 프로세서는( 그리고 그러므로 자기 스스로의 BIPI vector 를 수신한다. ), 자기 스스로를 BSP 로 선택하고 자신의 IA32_APIC_BASE MSR 에 있는 BSP flag를 세팅한다.

(See Appendix C.1, “Overview of the MP Initialization Process For P6 Family Processors,” for a description of the BIPI, FIPI, and SIPI messages.)

• 남은 논리 프로세서들은 ( NOP발생에 실패한 ) Aps로 설정된다. 그들은 자신들의 BSP flag 를 clear 상태로 만들고 “wait-for-SIPI 상태” 로 돌입한다.

• 가장 최근에 인정된 BSP는 “자신의 모든 것을 포함한” FIPI 메시지를 방송하며, 이는 BSP와 Aps 에게 MP 초기화가 끝난 signal로 여겨지게 된다. 오직 BSP flag 가 세팅된 프로세서만이 FIPI 메시지에 대답할 수 있다. 응답은 BIOS boot-strap code의 해석과 실행으로 수행되며, 시작지점은 reset vector ( 물리주소 FFFF FFF0H ) 이다.

5. boot-strap code의 부분으로, BSP는 ACPI 테이블, MP table 을 만들고 자신의 초기화된 APIC ID 이 테이블에 적절히 추가한다.

6. boot-strap 프로시저의 마무리에, BSP는 processor counter를 1로 세팅하고 SIPI 메시지를 모든 시스템 상의 APs 들에게 보낸다. 여기서, SIPI 메시지는 BIOS AP 초기화 코드의 vector를 포함하고 있다. ( 000VV000H 에 VV는 SIPI 메시지에 포함된 벡터 )

7. AP 초기화 코드의 첫 동작은 BIOS 초기화 semaphore 에 대한 AP들 간의 경쟁이다.

세마포어의 첫 번째AP가 초기화 코드를 수행하기 시작한다. (See Section 8.4.4, “MP Initialization Example,” for semaphore implementation details.)

AP 초기화 프로시저의 부분으로 AP는 자신의 APIC ID 넘버를 ACPI와 MP table에 적절하게 추가하고 processor counter를 1 증가시킨다(increments the processor counter by 1). 초기화 프로시저가 완료되고, AP는 CLI 명령을 수행하고 스스로 halts 된다.

8. 각 APs가 세마포어에 대한 접근 권한을 얻고 AP 초기화 코드를 수행할 때, BSP 는 시스템 버스에 연결되어 있는 프로세서의 숫자를 세고, BIOS boot-strap code가 완료되면 운영체제-시스템 boot-strap 과 start-up 코드를 실행하기 시작한다.

9. BSP 가 운영체제-시스템 boot-strap 과 start-up코드를 실행하는 동안, APs는 계속 halted 상태를 유지하고 있는다. 이 상태는 오직 INITs, NMIs, SMIs 에 대해서만 반응한다. 또한 STPCLK# pin에 따른 동작과 이를 살펴보는 것에도 반응한다.( They will also respond to snoops and to assertions of the STPCLK# pin.) 이어지는 섹션에서 MP 초기화 프로토콜이 다중 Intel Xeon 프로세서들에서 MP 설정을 하는 과정을 예제( 코드와 함께 )로 다룰 것이다.

Appendix B, “Model-Specific Registers (MSRs),” describes how to program the LINT[0:1] pins of the processor’s local APICs after an MP configuration has been completed.

8.4.4 MP Initialization Example

다음의 예는 MP 초기화 프로토콜이 BSP와 APs가 설정된 후에 MP 시스템에서 프로세서를 초기화 하는데 사용되는 과정을 그려보기 위함이다. 코드는 Intel 64나 프로토콜을 사용하는 IA-32 프로세서에서 동작하는 코드이다. 이는 P6 패밀리 프로세서를 포함하고, 펜티엄 4 프로세서들, 인텔 코어 듀오, 인텔 코어 2 듀오와 인텔 제온 프로세서들도 포함한다.

다음의 상수와 데이터 정의는 코드 예제와 함께 사용된다. 이들은 Table 10-1에서 정의된 APIC 주소들에 기반을 두고 있다. ( Table 10-1 은 별도 첨부 )

ICR_LOW EQU 0FEE00300H

SVR EQU 0FEE000F0H

APIC_ID EQU 0FEE00020H

LVT3 EQU 0FEE00370H

APIC_ENABLED EQU 0100H

BOOT_ID DD ?

COUNT EQU 00H

VACANT EQU 00H

8.4.4.1 Typical BSP Initialization Sequence

BSP와 APs 가 선택된 후에 (by means of a hardware protocol, see Section 8.4.3, “MP Initialization Protocol Algorithm for Intel Xeon Processors” ) 일반적인 IA-32 아키텍쳐라면BSP는 BIOS boot-strap code(POST) 를 실행하기 시작한다. 시작 주소는 (FFFF FFF0H). boot-strap code 는 일반적으로 다음과 같은 동작을 수행한다.

1. 메모리 초기화

2. microcode 로드와 프로세서로의 갱신

3. MTRRs 초기화.

4. caches 활성화

5. EAX 레지스터 0H 값과 함께 CPUID 명령을 실행한 뒤, EBX, ECX, EDX 레지스터를 읽고 BSP 가 “GenuineIntel”인지를 판단한다.

6. EAX 레지스터 1H 값과 함께 CPUID를 실행하고 EAX, ECX, EDX 레지스터에 있는 값을 램에 있는 시스템 설정 공간에 저장해서 나중에 사용한다.

7. AP가 실행하기 위한 start-up 코드를 메모리의 1MByte 하단 4-Kbyte page에 불러온다.

8. 보호 모드로 전환하고 APIC 주소 공간을 캐쉬할 수 없는 공간으로 맵한다.

9. local APIC ID 레지스터( 기본값 0 ) 에서 BSP의 APIC ID 를 결정, 하단의 코드 조각은 시스템 상의 논리적 프로세서에 적용할 예제이다. ( 메모리 맵 인터페이스를 사용해 APIC 레지스터에 access하는 (xAPIC 모드에서 동작하는Local APIC 유닛))

MOV ESI, APIC_ID; Address of local APIC ID register

MOV EAX, [ESI];

AND EAX, 0FF000000H; Zero out all other bits except APIC ID

MOV BOOT_ID, EAX; Save in memory

APIC ID를 ACPI 와 MP 테이블에 저장하고 선택적으로 램 상의 시스템 설정 공간에도 저장한다.

10. 4-KByte페이지의 베이스 주소를 AP의 bootup code를 위해 8-bit 벡터 값으로 바꾼다. 8-bit 벡터는 실제-주소 모드 주소 공간(1-MByte 주소) 에서의 4-Kbyte 페이지에 대한 주소의 정의다. 예를 들면 벡터 0BDH 는 start-up 메모리 주소 000BD000H를 나타낸다.

11. APIC spurious vector register (SVR)의 bit 8을 세팅해서 local APIC를 활성화 시킨다.

MOV ESI, SVR; Address of SVR

MOV EAX, [ESI];

OR EAX, APIC_ENABLED; Set bit 8 to enable (0 on reset)

MOV [ESI], EAX;

12. APIC 에러 핸들러에 8-bit vector로 LVT 에러 핸들링 엔트리를 설정한다.

MOV ESI, LVT3;

MOV EAX, [ESI];

AND EAX, FFFFFF00H; Clear out previous vector.

OR EAX, 000000xxH; xx is the 8-bit vector the APIC error handler.

MOV [ESI], EAX;

13. Lock 세마포어 변수 VACANT 를 00H로 초기화 한다. APs는 이 세마포어를 사용해서 BIOS AP 초기화 코드를 실행하는 순서를 결정할 수 있다.

14. 시스템 상에 APs의 존재와 프로세서의 숫자를 BSP가 탐지하게끔 다음에 오는 동작들을 수행한다.

— COUNT 변수를 1로 세팅한다.

— timer를 시작한다. ( 거의 100밀리세컨드 간격으로 ). AP BIOS 초기화 코드에서, AP는 COUNT 변수를 증가시켜 자신의 존재를 나타낸다. Timer가 만료되었을 때, BSP는 COUNT 변수를 체크한다. 만약 Timer가 만료되었고 COUNT 변수가 증가되지 않았다면, APs가 존재하지 않거나 뭔가 문제가 발생한 것이다.

15. INIT-SIPI-SIPI IPI 흐름을 방송해서 AP들이 깨어나게 하고 그들을 초기화 시킨다.

MOV ESI, ICR_LOW; Load address of ICR low dword into ESI.

MOV EAX, 000C4500H; Load ICR encoding for broadcast INIT IPI

; to all APs into EAX.

MOV [ESI], EAX; Broadcast INIT IPI to all APs

; 10-millisecond delay loop.

MOV EAX, 000C46XXH; Load ICR encoding for broadcast SIPI IP

; to all APs into EAX, where xx is the vector computed in step 10.

MOV [ESI], EAX; Broadcast SIPI IPI to all APs

; 200-microsecond delay loop

MOV [ESI], EAX; Broadcast second SIPI IPI to all APs

; 200-microsecond delay loop

Step 15:

MOV EAX, 000C46XXH; Load ICR encoding from broadcast SIPI IP

; to all APs into EAX where xx is the vector computed in step 8.

16. Timer 인터럽트를 기다린다.

17. COUNT 변수를 읽고 판단해서 프로세서의 개수를 결정한다.

18. 필요하다면, APIC를 재설정하고 남은 시스템 진단을 계속 수행한다.

8.4.4.2 Typical AP Initialization Sequence

AP가 SIPI 를 받으면, SIPI에 encode 되어있는 vector 에 있는 BIOS AP 초기화 코드를 실행하게 된다. AP 초기화 코드는 일반적으로 다음과 같은 동작을 수행한다.

1. BIOS 초기화 Lock Semaphore 를 기다린다. 세마포어의 제어권을 얻은 뒤, 초기화를 계속한다.

2. microcode update를 프로세서로 로드한다.

3. MTRRs을 초기화한다. ( BSP에서 사용됐던 맵핑 방식이 그대로 사용된다. )

4. 캐쉬를 활성화 한다.

5. EAX 레지스터 0H 값과 함께 CPUID 명령을 실행한 뒤, EBX, ECX, EDX 레지스터를 읽고 BSP 가 “GenuineIntel”인지를 판단한다.

6. EAX 레지스터 1H 값과 함께 CPUID를 실행하고 EAX, ECX, EDX 레지스터에 있는 값을 램에 있는 시스템 설정 공간에 저장해서 나중에 사용한다.

7. 보호 모드로 전환해서 APIC 주소 공간을 맵 하는걸 보장한다.

8. local APIC ID 레지스터로부터 AP의 APIC ID를 결정하고, 이를 MP와 ACPI 테이블에 추가하며 선택사항으로 RAM에 존재하는 시스템 설정 공간에 저장한다.

9. SVR 레지스터의 bit 8을 세팅해서 local APIC 의 초기화와 설정을 그리고 에러 핸들링을 위해 LVT3(에러 LVT)를 세팅한다. (as described in steps 9 and 10 in Section 8.4.4.1, “Typical BSP Initialization Sequence”).

10. AP들의 SMI 실행 환경을 설정한다. ( AP와 BSP는 반드시 각각의 다른 SMBASE 주소가 있어야 한다. )

11. COUNT 변수를 1 증가시킨다.

12. semaphore를 풀어준다.

13. CLI 와 HLT 명령어를 실행한다.

14. INIT IPI를 기다린다.

8.4.5 Identifying Logical Processors in an MP System

BIOS가 MP 초기화 프로토콜을 완료하고 난 뒤에, 각 논리적 프로세서는 자신의 local APIC ID로 유일하게 식별될 수 있다. 소프트웨어는 다음의 방법들로 APIC ID들에 접근할 수 있다.

• Read APIC ID for a local APIC — 논리 프로세서에서 실행 중인 코드는 local APIC unit이 x2APIC(see Intel® 64 Architecture x2APIC Specification) 모드인가 아니면 xAPIC 모드인가에 따라서 다른 방법으로 APIC ID를 읽을 수 있다.

— 만약 local APIC unit이 x2APIC 를 지원하고 x2APIC 모드에서 동작 중이라면, 32-bit APIC ID를 RDMSR 명령을 수행해서 프로세서의 x2APIC ID 레지스터를 읽어올 수 있다. 이 방법은 아래서 설명하는 CPUID (leaf) 0BH을 수행하는 방법과 동일하다.

— 만약 local APIC unit 이 xAPIC 모드에서 동작 중이라면, 8-bit APIC ID를 프로세서의 local APIC ID 레지스터를 MOV 명령을 수행해 얻을 수 있다. (see Section 10.4.6, “Local APIC ID”) 이것이 물리적인 목적지 모드 인터럽트들이 직접적으로 프로세서를 찾아갈 때 사용되는 ID이다. (This is the ID to use for directing physical destination mode interrupts to the processor.)

• Read ACPI or MP table — MP 초기 프로토콜의 부분으로, BIOS는 ACPI와 MP 테이블을 생성한다. 이 테이블들은 Multiprocessor Specification Version 1.4 에 정의되어 있으며 소프트웨어에게 시스템과 그들의 local APIC ID들에 있는 프로세서 리스트를 제공해준다. ACPI 테이블은 ACPI 명세에 따라 형식이 결정되고, 이에 대해서 산업표준전원관리와 MP 시스템들의 플랫폼 환경 명세가 있다.

• Read Initial APIC ID (만약 프로세서가CPUID leaf 0BH를 지원하지 않는다면) —

APIC ID는 전원인가 동안 논리 프로세서에게 배정된다. 이 초기 APIC ID는 CPUID.1:[31:24] 에 의해 보고된다. 그리고 local APIC에서 읽어 들인 현재 값과 다를 수 있다. 초기 APIC ID는 멀티-프로세서 시스템이 CPUID leaf 0BH를 지원하지 않을 때 논리 프로세서들간의 관계 topological을 알아내는데 사용될 수 있다.

초기 APIC ID의 비트 8-bit는 여러가지 비트 마스크를 나타낼 수 있다. 각 비트 마스크는 MP 시스템에서 멀티-쓰레딩 자원의 topology hierarchical level 을 나타내는 이를 식별하는데 사용할 수 있다. (See Section 8.9.1, “Hierarchical Mapping of Shared Resources”). 초기 APIC ID는 4비트-필드 이상으로 이루어져 있고, non-clustered MP 시스템이라면 3비트-필드 이상으로 이루어져 있다.

• Read 32-bit APIC ID from CPUID leaf 0BH (만약 프로세서가CPUID leaf 0BH를 지원한다면) — 유일한 APIC ID는 전원인가 동안 논리 프로세서에 배정된다. 이 APIC ID는 CPUID.0BH:EDX[31:0] 의 32-bit 값으로 전달받을 수 있다. 32-bit APIC ID와 CPUID leaf 0BH를 사용해서 논리 프로세서들 간에 관계 topological 관계를 확인할 수 있다. – CPU가 CPUID leaf 0BH 를 지원한다면 말이다. 32-bit x2APIC ID의 bit들을 CPUID leaf 0BH를 인자로 사용해 하위-필드를 더 추출할 수 있다. (See Section 8.9.1, “Hierarchical Mapping of Shared Resources”)

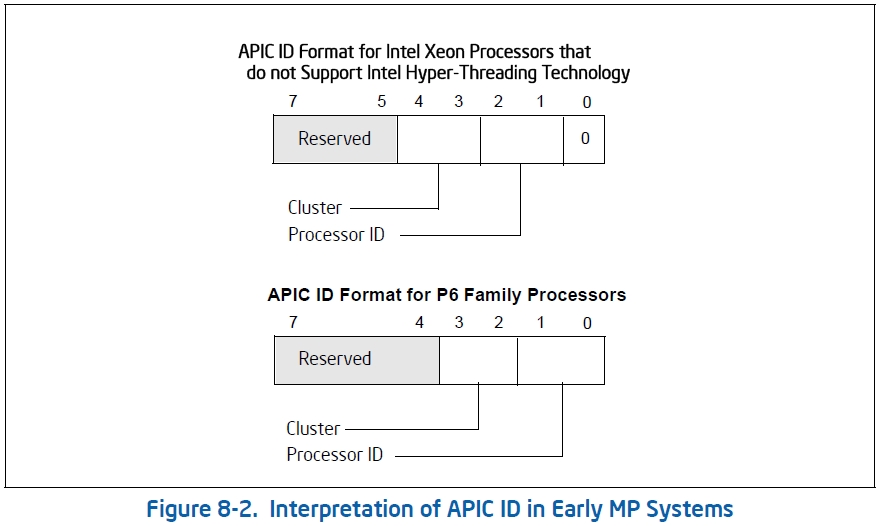

Figure 8-2는 먼저 등장했던 싱글코어 프로세서들의 APIC ID bit 필드의 두 예를 보여주고 있다. 싱글코어 인텔 제온 프로세서에서, 논리 프로세서는 전원인가 동안 APIC ID는 8-bit 배정받고 초기화된다. Bits 2:1은 2-bit 물리 패키지 식별자를 나타낸다. ( 이는 socket 식별자로도 생각될 수 있다. ) 시스템의 물리프로세서 설정이 clusters로 설정되었는지는, bits 4:3 2-bit cluster ID가 나타내준다. Bit 0은 인텔 제온 프로세서 MP 에서 두 논리 프로세서 패키지를 식별하기 위해 존재하지만(see Section 8.9.3, “Hierarchical ID of Logical Processors in an MP System”), 제온 프로세서는 인텔HT 기술을 지원하지 않기 때문에 항상 0이다. 인텔 제온 프로세서의 인텔 HT 기술을 지원을 위해서, bit 0 은 인텔 제온 프로세서 MP 와 같은 함수를 수행한다. 더 최근에 출시된 멀티 코어 프로세서들을 위해, Section 8.9,1 “Hierarchical Mapping of Shared Resources” 을 봐라. 논리적 프로세서들과 초기 APIC ID의 인텔 64와 IA-32 프로세서 패밀리의 bit 필드의 위치 사이에 대한 Topological 관계의 완전한 설명이 있다.

Bit 필드의 숫자와 bit-필드들의 넓이는 프로세서와 플랫폼 하드웨어에 의존적임을 알린다. 소프트웨어는 실행시간에 이들을 알아내야 한다. 초기 APIC ID들이 논리 프로세서들에게 배정되었을 때, 논리 프로세서에 배정되는 APIC ID의 값은 bit-필드의 경계크기와 코어, 물리 패키지, 기타 요소에 따라 변한다. 추가로 멀티-쓰레딩 가능 시스템의 초기 APIC ID 의 비트 필드 예제는 Section 8.9에서 볼 수 있다.

P6 패밀리 프로세서를 위해서, APIC ID는 전원인가 동안 4bits로 초가화 되어 배정된다. ( figure 8-2 ) 여기서 bits 0과 1 2-bit는 프로세서(or socket) 을, bit 2-3은 2-bit cluster ID를 나타낸다.

댓글 4

-

서태원

2010.11.04 11:23

-

박한범

2010.11.04 13:17

넵 말씀하신게 옳습니다.

이해 부탁드리는게 장님은 자기가 만지고 있는게 코끼리의 어느 부분인지 모른다는 겁니다.

제가 딱 그 상황인것 같네요.

위 글을 보시면 이런 부분이 있습니다. BSP가 bootstrap을 수행하고 AP는 halt 상태에 들어가고, INIT-SIPI 가 올때까지 잠수탄다는 내용입니다. OS에서도 이런 부분이 있을 거라고 예상됩니다. 스케쥴링을 보면 현재 쓰레드의 퀀텀을 감소시키고 때에 따라서 다음쓰레드로 문맥 전환이 이뤄지는 부분이 있습니다.

이 과정이 수행되기 위해서는 OS에서도 프로세서를 멀티코어를 관리할 수 있게 일련의 초기화 동작을 해줘야 될겁니다.

제 질문의 발단은 여기서 시작됐구요...

지금 답변을 보면 OS의 Start-up 코드를 언급하시는 것 같은데, 당시에는 이해대한 이해를 할 수가 없었습니다.

오로지 PRCB에 CPU를 연결할 단서를 찾는데 집중했기 때문인지도 모르겠습니다. 어쨌든 스케쥴링 알고리즘은 FS레지스터가 이용되는게 맞다고 생각하고 있습니다. 이는 제가 윈도우 스케쥴링 알고리즘에서 kiInterruptDispatch라는 Dispatch 인터럽트를 살펴봤기 때문에 어느정도 확신이 있죠. 하지만 CPU별로 FS레지스터와 같은 값을 초기화해주는 과정이 어떻게 동작하는지 상상하는것 조차 어려웠던 제 능력의 부재 때문에 문답이 길어졌기도 합니다.

끝까지 인내를 가지고 답변을 주신 분들께 정말 감사하는 이유기도 하구요. ^^; 어쨌든 그렇습니다.

못난 후배라고 생각하시고 앞으로도 많은 가르침 부탁드립니다.

-

백창우

2010.11.04 11:40

ㅎㅎ 고생많이 하셨습니다.

제가 말한 H/W 초기화 과정은 위 내용과 함께, kernel에서 부팅시 초기화 하는것도 포함됩니다.

그것도 찾아보시면 도움이 되실겁니다. 하지만 정확하게 알려면 굉장히 시간이 많이 걸리긴하죠.

그리고 저에게 질문하지 마세요.

저는 누가 대놓고 저에게 질문하는걸 별로 않좋아합니다.

좀 편안하게 놀려고 답변다는건데, 그것이 일이 되는건 싫습니다.

-

박한범

2010.11.04 13:18

물론입니다. ^^

단지 글의 제목을 이렇게 정한 이유는 답변을 계속 해주셨던 창우님에 대한 죄송함의 표현이기도 합니다.

그리고 감사하기도 하구요

.

첨부하시 내용은 boot과정에서 어떻게 해야하는 지를 써놓은 것이구요.

BIOS에서 수행해야 하는 내용입니다.

CPUID instruction은 BIOS code에서 사용을 해서 CPU detail에 대한 내용을 알수 있구요.

Linux kernel에서는 아마도 Local APIC에 있는 ID field를 이용해서 CPU를 식별할겁니다.

Process scheduling과는 크게 연관이 없는 내용인듯 합니다.