Chisel 사용법에 대한 정보를 하기와 같이 공유합니다.

▣ Chisel 3 설치

>>> Installation

▶ Overview

⊙ Chisel3 (Scala) to Firrtl (this is your "Chisel RTL").

⊙ Firrtl to Verilog (which can then be passed into FPGA or ASIC tools).

⊙ Verilog to C++ for simulation and testing using Verilator.

▣ Chisel Tutorials (Release branch)

>>> Getting the Repo

$ git clone https://github.com/ucb-bar/chisel-tutorial.git

$ cd chisel-tutorial

$ git fetch origin

$ git checkout release

Note: ./run-problem.sh, ./run-solution.sh, ./run-examples.sh are convenience scripts to invoke tests

$ ./run-examples.sh # shell script to execute one or more examples$ ./run-problem.sh # shell script to execute one or more problems$ ./run-solution.sh # shell script to execute one or more solutions$ ./run-problem.sh all or $ ./run-problem.sh Accumulator$ ./run-solution.sh all or $ ./run-solution.sh Accumulator$ ./run-examples.sh all or $ ./run-examples.sh Adder

▣ The Basics

>>> Running the Chisel Simulation $ ./run-examples.sh GCD

or $ ./run-examples.sh all

$ ./run-examples.sh GCD --backend-name verilator

or $ ./run-examples.sh all --backend-name verilator

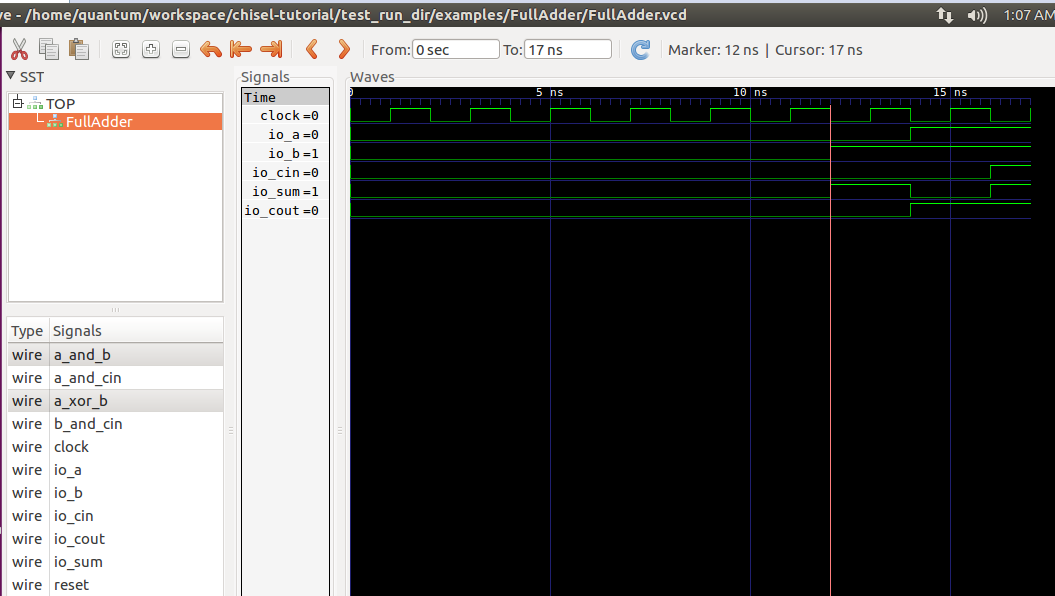

▷ GCD.v - Verilog representation of the Chisel circuit,

▷ GCD.vcd - waveform dump of the circuit signals during the simulation.

댓글 0

| 번호 | 제목 | 글쓴이 | 날짜 | 조회 수 |

|---|---|---|---|---|

| 공지 | [공지] MPSoC 스터디 관련 Q&A 게시판 입니다. | woos | 2016.04.09 | 240 |

| 5 | Verilog 책 소개... [1] | 상철 | 2010.04.05 | 11962 |

| 4 | xen source 다운로드 주소입니다. [1] | 백창우 | 2007.10.08 | 12494 |

| 3 |

powerpc assembly

[1] | 백창우 | 2007.07.15 | 12993 |

| 2 | panic... [2] | 송명환 | 2007.03.26 | 16553 |

| » |

[RISC-V] Chisel Tutorials (Release branch)

| 김남일 | 2018.09.01 | 50512 |

.